Zilog Z180

Der Zilog Z180 ist ein 8-Bit-Mikroprozessor, der 1985 unter der Bezeichnung HD64180 von der Firma Hitachi entwickelt wurde. Später baute die Firma Zilog Inc. den Chip nahezu unverändert unter der Bezeichnung Z180.

Befehlsstruktur

Der Z180 besitzt einen Prozessorkern, der vollständig Code-kompatibel zum Z80 ist. Erstmals kam hier die Microcode-Technik mit Execution-Pipelining zum Einsatz. Etliche Befehle brauchen weniger Maschinenzyklen als beim Original-Z80. Ein spezieller Interrupt, Reserved Instruction Trap, wird ausgelöst, wenn ein ungültiger Befehl erkannt wird. Die bei einigen Z80-Programmierern beliebten undokumentierten Befehle sind damit für den Z180 tabu. Neu hinzugekommen sind spezielle Instruktionen zur Adressierung der internen Register sowie ein Multiplikationsbefehl.

Peripherie

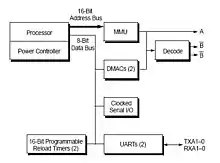

Der Erfolg des Z180 ist vor allem darin begründet, dass eine Reihe von Peripheriebausteinen bereits auf dem Chip integriert sind. Das sind im Einzelnen:

- Taktgenerator. Nur ein Quarz und zwei Kondensatoren sind erforderlich.

- Speicherverwaltung (Memory Management Unit, MMU) für 1 MByte Arbeitsspeicher.

- Zwei DMA-Controller mit Speicher<->Speicher und Speicher<->IO - Transfers. Die DMA-Controller unterstützen den vollen 1 MByte-Adressraum.

- Programmierbarer Wait-State-Generator, getrennt für Speicher und IO-Zugriffe

- Programmierbarer DRAM-Refresh-Controller

- Zwei asynchrone, serielle Vollduplex-Schnittstellen (UART) mit programmierbarem Baudraten-Generator für Übertragungsraten von 300 bis 38400 Baud und Unterstützung von Modem-Steuerleitungen

- Eine getaktete, serielle Hochgeschwindigkeits-Schnittstelle zum Aufbau von Multiprozessor-Systemen

- Zwei 16-Bit programmierbare Zeitgeber (Timer)

- Zwei externe universelle Interrupt-Eingänge

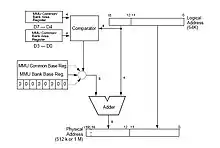

Speicherverwaltung

Da der Z80 maximal 64 kByte logisch adressieren kann, verwaltet die MMU den Arbeitsspeicher über sog. Speicherbänke. Es werden drei Bereiche unterschieden:

- Common Area 0

- Bank Area

- Common Area 1

Die MMU blendet den physikalischen Speicher in 4 kByte-Blöcken in den logischen Adressraum ein. Common Area 0 und 1 liegen jeweils am unteren und oberen Ende des logischen Adressraums und sind normalerweise festen physikalischen Speicherbereichen zugeordnet. Im dazwischenliegenden Bankbereich (Bank Area) kann das Programm bei Bedarf die Zuordnung des logischen Speichers umschalten.