Silizium-Durchkontaktierung

Unter dem Begriff Silizium-Durchkontaktierung (englisch through-silicon via, TSV) versteht man in der Halbleitertechnik eine meist vertikale elektrische Verbindung aus Metall durch ein Silizium-Substrat (Wafer, Chip). Die TSV-Technologie ist eine vielversprechende Möglichkeit zur Realisierung elektrischer Verbindungen zwischen Teilchips bei der 3D-Integration von zukünftigen integrierten Schaltkreisen (IC).

Einteilung

Bedingt durch den Herstellungsprozess lassen sich TSVs in drei Klassen einteilen: Via-first TSVs werden vor den aktiven Bauelementen (Transistoren usw., auch als Front-End of Line, FEOL, bezeichnet) prozessiert. Via-middle TSVs strukturiert man nach den aktiven Bauelementen, aber vor deren Verdrahtung (Metallisierung, auch als Back-End of Line, BEOL, bezeichnet). Via-last TSVs werden schließlich nach (oder während) des Aufbringens der Verdrahtungsmetallisierung, also dem BEOL, implementiert.[1][2]

Via-middle TSVs sind aktuell die meist genutzte Variante für moderne 3D-ICs als auch für Interposer-Aufbauten.[1][3]

Prozess-Technologie

Herausforderungen bestehen unter anderem in der finalen Prüfung der Teilchips nach dem Packaging im Fall der 3D-Integration. Für gewöhnlich wird ein Chip auf einem Chip-Carrier untergebracht und die Abschlussprüfung für den Endkunden wird nach dem Bonden durchgeführt. Im Fall von 3D-integrierten Chips die z. B. Silizium-Durchkontaktierungen verwendet, könnte so nur der 3D-Chip geprüft werden, da die Schnittstellen der Schaltungen auf den Teilchips in der Regel nicht nach außen geführt werden. Somit müssen Wege gefunden werden, den Abschlusstest für die Teilchips rechtzeitig durchzuführen oder die Bewertungen müssen sich auf die Ergebnisse des letzten elektrischen Tests am Ende der BEOL-Prozesses (vor Bump und dem Zerteilen des Wafers) beschränken.

Anwendung

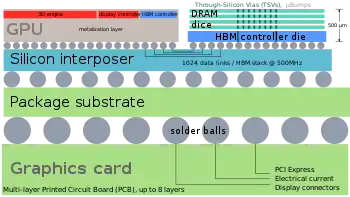

Bei einem 3D-integrierten Schaltkreis (3D-IC) handelt es sich um einen integrierten Schaltkreis, der aus einem vertikalen Stapel von abgedünnten Einzelchips besteht. Er erscheint nach außen wie ein monolithischer Schaltkreis, ist aber streng genommen eher ein Hybridschaltkreis der deutlich stärker integriert als typische Hybridschaltkreise. Insgesamt möchte man mit dieser 3D-Integration eine noch höhere Funktionalität der ICs bei gleicher Gehäusegrundfläche erreichen. Die Durchkontaktierung mit Hilfe von TSVs verbindet die einzelnen Chipebenen im 3D-ICs. TSV stellt dabei die derzeit aussichtsreichste Technik dar, um die hohen Anforderungen (kurz, robust usw.) an die elektrischen Pfade zu realisieren.[4]

Eine weitere Anwendung sind sogenannte 3D-Gehäuse (System-in-Package, Multi-Chip-Modul etc.). Sie enthalten zwei oder mehr ICs, die platzsparend vertikal gestapelt sind. Eine alternative Variante eines 3D-Gehäuses ist IBMs „Silicon Carrier Packaging Technology“, bei der die ICs nicht gestapelt werden, sondern ein Trägersubstrat mit TSVs versehen wurde und genutzt wird, um mehrere ICs in einem Gehäuse miteinander zu verbinden. Anders als in den meisten 3D-Gehäusen werden die gestapelten Chips daher nicht durch elektrische Verbindungen an den Seiten verdrahtet; Verdrahtungstechnik erhöht etwas die Länge und Breite des Pakets und erfordert in der Regel eine zusätzliche „Interposer“-Schicht zwischen den Chips. Bei der Verdrahtung über TSVs wurden diese Verdrahtungen über die Seiten gegen Durchkontaktierungen ausgetauscht, um die vertikalen Verbindungen über die Chipfläche verteilt herzustellen. Vorteile sind vor allem robustere Verbindungen und nochmals reduzierte Bauhöhen. Nachteilig kann der Verlust an Chipfläche durch die zusätzlichen TSVs sein. Diese Technik wird manchmal auch als Through-Silicon Stacking oder Thru-Silicon Stacking (TSS) bezeichnet.

Quellen

- Applied Materials Leads the Way to Enable TSV Interconnects for 3D Chip Stacking. Business Wire, 12. Juli 2010 (Pressemeldung von Applied Materials).

Literatur

- Vasilis F. Pavlidis, Eby G. Friedman: Three-dimensional integrated circuit design. Morgan Kaufmann, 2009, ISBN 978-0-12-374343-5, S. 48 ff. (eingeschränkte Vorschau in der Google-Buchsuche – In dem Buch finden sich neben anschaulichen Abbildungen zu TSV auch gute Abbildungen zu den anderen 3D-Integrationsverfahren).

Weblinks

- Through-Silicon Via 3D Integration (PDF; 86 kB). Applied Materials, 25. Januar 2010.

Einzelnachweise

- J. Knechtel, et al.: Large-Scale 3D Chips: Challenges and Solutions for Design Automation, Testing, and Trustworthy Integration. In: IPSJ Transactions on System LSI Design Methodology. 10, 2017, S. 45–62. doi:10.2197/ipsjtsldm.10.45.

- J. Lienig, M. Dietrich (Hrsg.): Entwurf integrierter 3D-Systeme der Elektronik. Springer, 2012, S. 11, 147, ISBN 978-3-642-30571-9.

- E. Beyne: The 3-D Interconnect Technology Landscape. In: IEEE Design Test. 33, Nr. 3, Juni 2016, ISSN 2168-2356, S. 8–20. doi:10.1109/mdat.2016.2544837.

- Through-Si Via (TSV), 3D Stacking Technology. In: International Technology Roadmap for Semiconductors 2009 Edition. Interconnect. 2009, S. 37–42 (PDF).