Shannon-Zerlegung

Die Shannon-Zerlegung oder Shannon-Expansion (benannt nach Claude Elwood Shannon) stellt eine Möglichkeit dar, boolesche Funktionen mithilfe ihrer sogenannten Kofaktoren darzustellen. Die mathematische Aussage über diese Zerlegung wird auch als Entwicklungssatz von Shannon bezeichnet. Obwohl der Satz nach Shannon benannt ist, der ihn erstmals 1949 verwendete,[1] wurde er bereits etwa hundert Jahre zuvor von George Boole aufgestellt.[2]

Aussage

Eine beliebige boolesche Funktion kann folgendermaßen zerlegt werden:

oder kürzer unter Verwendung der sogenannten Kofaktoren:

Die Kofaktoren und werden dabei durch partielle Auswertung von , d. h. Einsetzen der Variable definiert:

Diese Zerlegung wird auch als If-then-else-Normalform (INF) bezeichnet. Man sagt auch, die Funktion wird „nach entwickelt“. Wiederholt man die Anwendung des Satzes für eine beliebige Funktion auf alle ihre n Parameter, so gelangt man zu einer Darstellung der Funktion, welche ausschließlich die Operatoren ∧, ∨ und ¬ verwendet. Die rekursive Anwendung der Shannon-Zerlegung liefert also einen Beweis, dass sich jede boolesche Funktion mittels der Operatoren ∧, ∨ und ¬ ausdrücken lässt.

Diese Zerlegung führte unter anderem zur Entwicklung von binären Entscheidungsdiagrammen und damit zu einer der Möglichkeiten der Bearbeitung des Erfüllbarkeitsproblems der Aussagenlogik. Darüber hinaus kann der Entwicklungssatz etwa zur Herleitung klammerfreier Ausdrücke verwendet werden.

Beispiel

Gegeben sei die Boolesche Funktion .

Diese soll zunächst nach , dann nach und schließlich nach entwickelt werden:

| (Entwicklung nach ) | |||

| (Entwicklung nach ) | |||

| (Entwicklung nach ) | |||

| (Anwendung des Distributivgesetzes) |

Darstellung als Diagramm

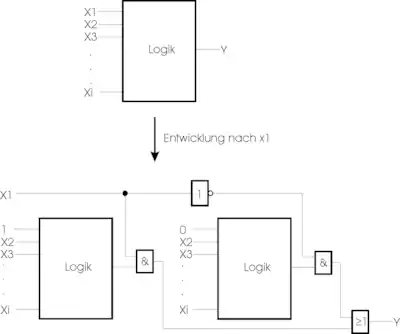

Man kann die Umformung auch als Multiplexer aus einem Nicht-Gatter, zwei UND sowie einem ODER-Gatter verstehen. Das Signal, nach dem die Zerlegung durchgeführt wird, ist das Steuersignal für den Multiplexer. Gemultiplext werden die beiden Ausgänge der gedoppelten Logik, wobei die eine Logik an dem entwickelten Eingang mit einer „1“ beaufschlagt wird, während die andere mit einer „0“ beaufschlagt wird. Als Diagramm dargestellt, sieht dies folgendermaßen aus:

Einzelnachweise

- C. E. Shannon: The synthesis of two-terminal switching circuits. In: Bell System Technical Journal. Band 28, Nr. 1, 1949, S. 59–98.

- G. Boole: The calculus of logic. In: Cambridge and Dublin Mathematical Journal. Band 3, Nr. 1848, 1848, S. 183–198 (PDF [abgerufen am 26. November 2012]).