MLC-Speicherzelle

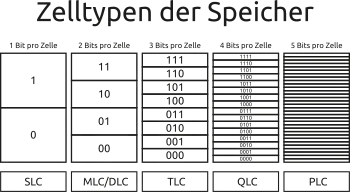

MLC-Speicherzellen (MLC kurz für englisch multi-level cell) sind Speicherzellen, in denen mehr als ein Bit pro Zelle gespeichert wird.

Um das zu ermöglichen, wird die in einer Speicherzelle hinterlegte Ladungsmenge feiner dosiert und beim Auslesen auch genauer ausgewertet, um mehr als zwei mögliche Zustände zu unterscheiden und mehr als ein Bit abspeichern zu können. Speicher mit nur einem Bit pro Zelle wird als single-level cell (SLC) bezeichnet.

Das Abspeichern mehrerer Bits pro Speicherzelle hat den Nachteil, dass im Allgemeinen die Lese- und Schreibgeschwindigkeit geringer ist. Die Zellen reagieren wesentlich empfindlicher auf Ladungsverluste. Geringe Ladungsverluste von 10 Prozent, die bei SLCs keinerlei Rolle spielen, verursachen bei Zellen mit 8 möglichen Zuständen Bitfehler.

Es werden die gleichen Fehlerkorrekturverfahren wie in SLCs eingesetzt, allerdings mit einem höheren Kontingent an Korrekturdaten, was den Gewinn an Kapazität wieder etwas schmälert. In der Regel kommen hier BCH-Codes (Bose-Chaudhuri-Hocquenghem-Codes) zur Anwendung.

Flash-Speicher

Die Technik wird vor allem bei NAND-Flash-Speichern verwendet, in denen pro Speicherzelle, welche aus einem MOSFET mit Floating-Gate besteht, mehrere Bits – Stand 2009 bis zu vier (Quad Level Cell,[1] auch Quadruple Level Cell) – gespeichert werden können. Dadurch wird die Speicherdichte erhöht. Seit dem Aufkommen von Speicherzellen, die drei Bits pro Zelle speichern können (TLC-Speicherzellen) wird die Bezeichnung MLC-Speicherzelle fälschlicherweise oft synonym für 2-Bit-Speicherzellen verwendet.[2]

Da MLC-Speicher bei gleicher Speicherkapazität weniger Chipfläche benötigt, ist diese Technik deutlich günstiger als SLC-Speicher und wird vorwiegend bei leseintensiven Speicheranforderungen benutzt. Bei Produkten, die auf Flash-Speichern basieren (z. B. USB-Sticks), können die Abkürzungen SLC oder MLC in der Produktbezeichnung Hinweise auf die Verwendung von SLC oder MLC geben.

Hintergrund

| MLC-Zelle | SLC-Zelle | |||||

|---|---|---|---|---|---|---|

| Nenn- wert |

Schwell- wert |

Binär- wert |

Nenn- wert |

Schwell- wert |

Binär- wert | |

| 10 kΩ | 00 | 10 kΩ | 0 | |||

| 32 kΩ | ||||||

| 100 kΩ | 01 | |||||

| 320 kΩ | 320 kΩ | |||||

| 1 MΩ | 10 | 10 MΩ | 1 | |||

| 3,2 MΩ | ||||||

| 10 MΩ | 11 | |||||

In vielen Speicherbausteinen wird in jeder Speicherzelle ein Bit gespeichert, z. B. in DRAMs, indem in der Zelle einer von zwei möglichen Zustände abgespeichert wird. Dabei ist einem Zustand eine logische 0, einem zweiten Zustand eine logische 1 zugeordnet. Im DRAM entspricht eine Spannung von 0 V in der Zelle der logischen 0, eine Spannung in Höhe der Spannung VBLH (engl. voltage bit line high) der logischen 1.

Bei verschiedenen Speichertechnologien ist es möglich, mehr als zwei Zustände der Speicherzelle zu unterscheiden und diesen entsprechend mehr als ein Bit zuzuordnen. Das wird bisher vor allem bei Flash-Speichern angewendet, allerdings wird auch für weitere Speichertypen an diesem Thema geforscht.

Beispielsweise kann bei PCRAM eine Speicherzelle Widerstandswerte in einem weiten Bereich annehmen, z. B. von 10 kΩ bis 10 MΩ. Damit könnten folgende Zuordnungen zu Bit-Werten und die Schwellwerte zwischen den Zuständen definiert werden, so dass pro Zelle mehrere Bits abgespeichert werden (siehe Tabelle).

Vor- und Nachteile

Der wesentliche Vorteil bei Multi-Level-Speicherung ist die höhere Speicherdichte, da hier mehr als ein Bit pro Zelle abgespeichert wird. Somit kann auf der gleichen Chipfläche die doppelte (oder eine noch höhere) Informationsmenge gespeichert werden als in einem Speicher mit Single-Level-Speicherung. Insbesondere bei Halbleiterspeichern bietet das erhebliche Kostenvorteile, da die benötigte Chipfläche ein wesentlicher Kostenfaktor bei der Herstellung ist.

Nachteilig bei Multi-Level-Speicherung ist, dass einerseits die Bewertung des Speicherinhalts langsamer geschieht – da der Abstand zum Schwellwert kleiner ist – und mit aufwändigeren Schaltungen durchgeführt werden muss. Aufgrund des geringeren Abstands zum Schwellwert ist auch die Fehleranfälligkeit größer, da im Vergleich zur Single-Level-Speicherung kleinere Veränderungen des Speicherzustandes reichen, um in einen benachbarten Zustand zu fallen und damit ein oder mehrere Bits zu verändern. Im Vergleich zur Single-Level-Speicherung sind komplexere Fehlerkorrekturverfahren zum Sichern des Informationsgehalts der Daten erforderlich, in der Regel werden bei Flash-Speichern BCH-Codes eingesetzt. Auf Systemebene wird dadurch eine vergleichbare Zuverlässigkeit erreicht.[3][4]

Einzelnachweise

- Vier Bits pro Flash-Speicherzelle

- vgl. Rino Micheloni, Alessia Marelli, Kam Eshghi: Inside Solid State Drives (SSDs). Springer, 2012, ISBN 978-94-007-5146-0, S. 60 ff. (eingeschränkte Vorschau in der Google-Buchsuche).

- Google test finds all SSDs are created equal, in some ways. Tests puncture the myth of SLC durability. Network World, 2. März 2016, abgerufen am 4. März 2016 (englisch).

- Schroeder, Lagisetty, Merchant: Flash Reliability in Production: The Expected and the Unexpected. (PDF) USENIX, 22. Februar 2016, abgerufen am 4. März 2016 (englisch).