Lockstep (Computertechnik)

Der Begriff Lockstep beschreibt im Bereich der Computertechnik, insbesondere bei Prozessoren und Mikrokontrollern, eine Methode zur Fehlertoleranz und Fehlererkennung in der Hardware, welche durch den Einsatz mehrerer gleicher oder gleichartiger Einheiten wie CPU-Kerne in Mehrkernprozessoren erreicht wird.[1] Der Name des Verfahrens leitet sich von dem Begriff englisch lockstep marching ab, einem bei Militär und in manchen Gefängnissen anzutreffenden engen Gleichschritt. Prozessoren im Lockstepbetrieb, wie beispielsweise darauf ausgelegte ARM Cortex-R oder die Serie MPC57xx PowerPC-Prozessoren, werden vor allem in sicherheitskritischen Anwendungen wie Motorsteuerungen (ECU) von Fahrzeugen und in autonomen Triebwerksregelungen (FADEC) von Flugzeugen eingesetzt.

Verfahren

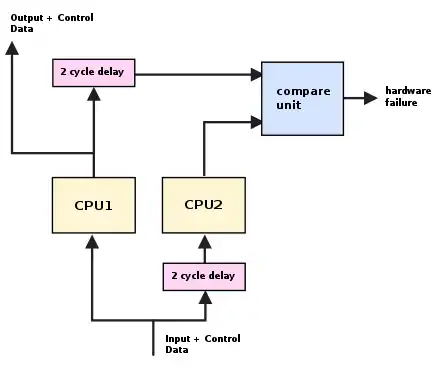

Der Prozessoraufbau ähnelt bei Lockstep den von Parallelrechnern, allerdings dient die Parallelschaltung nicht der Leistungssteigerung der Rechenleistung, sondern alle CPU-Kerne arbeiten das exakt gleiche Programm oder den gleichen Algorithmus ab. Die Kontrolle und Bewertung durch Vergleich der Ergebnisse der einzelnen CPU-Kerne erfolgt daran anschließend in einzelnen, zeitlich engen und nicht unterbrechbaren Schritten (englisch step). Durch die so erzielte Redundanz lassen sich hardwareseitige Ausfälle in einem der Prozessorkerne detektieren und darauf reagieren, wie dies bei einem Dual-Core im Lockstep-Betrieb der Fall ist, oder durch Mehrheitsentscheidungen Fehler nicht nur Erkennen, sondern in gewissen Umfang auch korrigieren, wie dies bei Triple-Core-Prozessoren bei einem Einzelfehler der Fall ist.

Um Störungen, welche auf alle parallel betriebenen Prozessorkerne gleichmäßig und gleichzeitig einwirken, dieser Fall wird als sogenannter Ausfall mit gemeinsamer Ursache bezeichnet, sicher erkennen zu können, werden die einzelnen Prozessoren um einige wenige Taktzyklen zeitlich versetzt betrieben. Dadurch wirkt sich die gemeinsame Störungsursache in unterschiedlichen Zuständen der einzelnen Cores aus und lässt sich so im anschließenden Vergleich der Ergebnisse als Abweichung feststellen.[2]

Die Fehlererkennung beschränkt sich bei diesem Verfahren auf die Erkennung und ggf. Korrektur von hardwarebedingten Ausfällen im elektronischen Bauelement, auf Single Event Upsets (SEU) oder Latch-Up-Effekten in einen der CPU-Kerne oder im Bereich der getrennt ausgeführten Stromversorgung. Systematische Fehler im Programmcode oder Entwicklungsfehler im Algorithmus lassen sich mit Lockstep grundsätzlich nicht erkennen oder kompensieren.

Literatur

- Hans-Leo Ross: Functional Safety for Road Vehicles: New Challenges and Solutions for E-mobility and Automated Driving. Springer, 2016, ISBN 978-3-319-33360-1.

- A. Avizienis, H. Kopetz, J.C. Laprie: The Evolution of Fault-Tolerant Computing. Springer Science & Business Media, 2012, ISBN 978-3-7091-8871-2.

Einzelnachweise

- M. Baleani et al.: Fault-Tolerant Platforms for Automotive Safety-Critical Applications. (Nicht mehr online verfügbar.) International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES), 30. Oktober 2003, archiviert vom Original am 9. August 2017; abgerufen am 8. März 2018 (Chapter 3: A Survey of Fault-Tolerant Multi-Processor Architectures). Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis.

- Safety Manual for MPC5744P. NXP (Firmenschrift), abgerufen am 17. März 2020 (Chapter 3.2: Dual-core lockstep).