HDI-Leiterplatte

Die HDI-Leiterplatte (High-Density-Interconnect-Leiterplatte) ist eine kompakt gestaltete Leiterplatte.

Vorteile gegenüber gewöhnlichen Leiterplatten

Die ständig fortschreitende Miniaturisierung und die immer komplexer benötigten Schaltungen sowie Bauelemente mit hohen Pin-Zahlen bringen die klassischen Multilayer-Platinen immer mehr an die physikalischen Grenzen ihrer Möglichkeiten. HDI-Leiterplatten bieten feinere Leitungsstrukturen und kleinere Durchkontaktierungen. Die Microvias schaffen so Platz und haben zudem bessere elektrische Eigenschaften als klassische „dicke“ Durchkontaktierungen oder Sacklöcher.

Durch die Verpressung weiterer Lagen mit der SBU-Technik (Sequential Build Up) lassen sich Signale auf den inneren Lagen verbinden und entflechten, ohne dabei den Platz für Bauteile mit hoher Pin-Dichte zu blockieren. Mit etwas Erfahrung können mit einem guten Layout diese Bauteile sogar überlappend gegenüber auf der Leiterplatte platziert werden. Dünne Leiterplatten mit 100-µm- und 125-µm-Strukturen ermöglichen dabei impedanzkontrollierte Leitungen für hohe und höchste Frequenzen.

Der Siegeszug der HDI-Leiterplatte startete Ende der 1990er Jahre mit den Produkten im DECT-Gigaset Pocket 2000 und im Siemens C+S25 GSM-Mobilfunk-Bereich. Die Leiterplatten stammten aus dem damaligen ppe-Werk in Schopfheim (heute gehört das Werk zum Würth Konzern) und später aus Pulversheim auch von der AT&S Leoben. 2008 werden weltweit etwa 98 Prozent aller mobilen GSM- und UMTS-Geräte als HDI-Leiterplatte gefertigt.

Nachteile gegenüber gewöhnlichen Leiterplatten

Aufgrund des komplexeren Herstellungsverfahrens ist man stärker an einen Hersteller gebunden (Beherrschte Fertigungsprozesse, Toleranzen, Schichtdicke, Dielektrizitätszahl des Trägermaterials etc.). Hochfrequenzanwendungen mit Striplines, lassen sich nicht bei den hohen Toleranzen in den Mikrovialagen realisieren. Hierzu ist eine weitere Lage erforderlich. Die Bezugslage der Stripline darf nicht in der 2. Kupferlage (Cu) unterhalb der Stripline liegen.

Aufbau und Fertigungsschritte

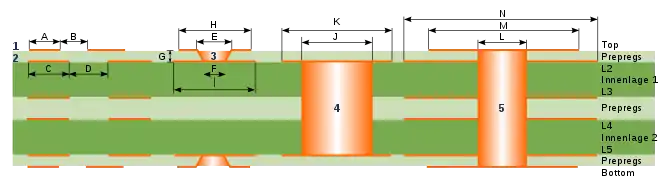

Zu Abbildung ganz oben. Abbildung ist eine schematische Darstellung. Auf Lagen mit galvanischer Aufkupferung (Buried Vias) können keine Kerne (Cores) verwendet werden. Die Strukturierung erfolgt erst nach dem LBA / Durchkontaktierungs Prozess.

| Symbol | Signatur | Beschreibung | Layoutvorgaben | Bemerkung |

|---|---|---|---|---|

| 1 | Außenlagenstrukturen | |||

| A | Außenlagenstruktur | > 75 µm | Abhängig von der Cu-Dicke | |

| B | Leiterbahnabstand | > 75 µm | Abhängig von der Cu-Dicke | |

| 2 | Innenlagenstruktur | |||

| C | Leiterbahnbreite | > 75 µm | Abhängig von der Cu-Dicke | |

| D | Leiterbahnabstand | > 75 µm | Abhängig von der Cu-Dicke | |

| 3 | Microvias von Top auf L2, Standard- o. kon. Micro Drill Werkzeug | |||

| E | Hole-Durchmesser Eintritt | > 100 µm | Wenn konisch, dann abhängig von Bohrtiefe (Dielektrikumsdicke) | |

| F | Hole-Durchmesser Targetpad | > 100 µm | Wird durch Werkzeug definiert | |

| G | Bohrtiefe | Abhängig von Dielektrikumsdicke | Aspect Ratio > 1:1 beachten! | |

| H | Microvia Eintrittspad | > E + 200 µm | Umlaufend 100 µm um Bohrung nötig | |

| I | Microvia Landepad | > 350 µm | F + 125 µm umlaufend um Hole-Durchmesser auf Landepad | |

| 4 | Buried Via von L2 auf L5 | |||

| J | Bohrdurchmesser | > 150 µm | Aspect Ratio > 1:8 beachten! | |

| K | Paddurchmesser | > L + 200 µm | ||

| 5 | Durchgangsloch | |||

| L | Bohrdurchmesser | > 150 µm | Aspect Ratio > 1:8 beachten! | |

| M | Paddurchmesser Außenlagen | > L + 200 µm | Umlaufend 100 µm um Bohrung nötig | |

| N | Paddurchmesser Innenlagen | > L + 250 µm | Umlaufend 125 µm um Bohrung nötig |

Stichwörter aus dem HDI-Bereich

- Blind Via (Sackloch)

- Auf einer Innenlage endende Ankontaktierung

- Buried Via (Vergrabene Durchkontaktierung)

- in den Kernlagen liegende und außen nicht sichtbare Durchkontaktierung

- HDI (High Density Interconnect)

- Schaltung mit Microvias und feinsten Strukturen

- Microvia

- An- oder Durchkontaktierung mit einem Durchmesser unter 200 µm

- SBU (Sequential Build Up)

- Sequentieller Lagenaufbau: bedingt mindestens zwei Pressvorgänge bei Multilayerschaltungen

- LBA (Leiterbild-Aufbau)

- Aufbringen von galvanischem Kupfer um Durchkontaktierungen herstellen zu können

Fertigung eines 6-Lagen-HDI/SBU-Multilayer

- Strukturen der Innenlagen 1 und 2 fertigen mit L2+L3 und L4+L5 (vgl. Bild oben)

- Verpressen der Innenlagen 1 und 2 mit den innen liegenden Prepregs zu einem Multilayer-Kern

- Bohren der Buried Vias als durchgehende Bohrungen (4)

- Durchkontaktierung des Multilayer-Kerns (L2 bis L5)

- Hole Filling (optional): Füllen der Hülse 4 mit Füllmaterial und anschließendes Planschleifen

- Strukturieren des Kerns (Lagen 2 und 5)

- Verpressen mit den außen liegenden Prepreg-Laminaten

- Bohren der Microvias 3 und der Durchkontaktierungen 5

- Fertigstellen (Strukturieren, Kontaktieren, Außenflächenbehandlung) wie eine gewöhnliche Multilayer

- Oberflächenfinish (empfehlenswert: chemisch Zinn oder chemisch Nickel/Gold)

Je nach den gewünschten Eigenschaften und nach der Lage und Art der Kontaktierungen sind mehrere Varianten des Aufbaus für eine bestimmte Lagenanzahl möglich.

Prüfen von HDI-Leiterplatten

Kleinere Serien

Kleinere Serien werden am wirtschaftlichsten mit Fingertestern (auch als Flying-Probe-Tester bekannt) geprüft, welche die Testpunkte optisch erfassen können und so ihre Prüffinger exakt auf die Pads auslenken können. Ein Vorteil ist dabei, dass der Fingertester einfach auf ein neues Produkt umgelernt werden kann. So können kleine Serien auch kostengünstig geprüft werden. Nachteil dabei ist, dass das Prüfen einer Leiterplatte mehrere Minuten in Anspruch nehmen kann, wenn viele Verbindungen zu prüfen sind. Oft werden aus Zeitgründen nur Impedanzmessungen gemacht und so wird der Prüfling nicht einer 100-%-Prüfung unterzogen.

Größere Serien

Bei größeren Serien (teilweise schon ab 50 bis 100 Leiterplatten) ist der Einsatz eines Starrnadeladapters sinnvoll. Dabei werden die Leiterplatten unter einem PRS (Kamerasystem) ausgemessen (auf Schrumpfung, Dehnung, Kissenform, Tonnenform, Verdrehung und Versatz zwischen dem Top- und Bottom-Layer). Anhand dieser Korrekturwerte wird dann die HDI-Leiterplatte in der Kontaktierung positioniert und mit dem Starrnadeladapter kontaktiert und geprüft. Mit den feinen Starrnadeln können 70 µm Strukturen kontaktiert werden, welche einen Prüfabstand > 150 µm aufweisen. Das Konzept dieser Adapter ermöglicht es, bis zu 280 Testpunkte pro cm² aufzulösen, wodurch eine sehr hohe Prüfdichte erreicht werden kann.

Vorteile sind:

- Das Prüfen mit Starrnadeladaptern ist sehr schnell, so dass auch größere Serien schnell geprüft werden können.

- Die HDI-Leiterplatten werden einer 100-%-Prüfung unterzogen

- Mit Starrnadeladaptern können auch bestückte HDI-Leiterplatten kontaktiert werden, wodurch so zusätzlich ein Funktionstest durchgeführt werden kann.

Nachteil ist, dass Starrnadeladapter produktspezifisch hergestellt werden müssen, wodurch pro Leiterplattentyp Adapterkosten entstehen.

Weblinks

- Zeitschrift productronic, 06/2002: Kostengünstig in die dritte Dimension (PDF-Datei; 49 kB)

- Multi-CB Leiterplatten: Begriffserklärung und Vorteile von HDI-Leiterplatten