Clock-Gating

Clock-Gating ist eine bei elektronischen synchronen Digitalschaltungen gebräuchliche Methode, um das Taktsignal in einzelnen Schaltungsteilen selektiv aus- und einzuschalten und so die mittlere Leistungsaufnahme der integrierten Schaltung (IC) zu reduzieren.

Allgemeines

Synchrone Digitalschaltungen wie beispielsweise übliche Mikroprozessoren bestehen aus einer Vielzahl von taktflankengesteuerten Flipflops, welche alle von einem zentralen Taktsignal, dem Systemtakt, getaktet werden. Im Regelfall werden nicht alle Funktionseinheiten in einem Mikrochip bei jedem Taktflankenzeitpunkt tatsächlich benötigt – beispielsweise, weil auf externe Ereignisse gewartet wird oder bestimmte Funktionseinheiten für eine bestimmte Aufgabe nicht benötigt werden. Bei Clock-Gating werden an geeigneten Stellen im Taktverteilungsnetz im Mikrochip sogenannte Torschaltungen, englisch gates, vorgesehen, welche die Taktdurchleitung zu den nicht benötigten Funktionseinheiten unterbinden können.

Der Hintergrund liegt in der CMOS-Technik, in der die digitalen Schaltungen gefertigt werden. Diese Technologie weist eine von der Schalthäufigkeit stark abhängige Verlustleistung auf – je höher die Taktfrequenz, desto höher die Verlustleistung, so der Takt immer eingeschaltet ist. Durch das Clock-Gating wird in nicht benötigen Funktionseinheiten die Anzahl der durchschnittlichen Umschaltvorgänge reduziert, was die mittleren Schaltverluste der gesamten Schaltung reduziert.

Der eigentliche Schaltvorgang im Clock-Gate hat so zu erfolgen, dass dabei kein Glitch auftritt.

Anwendungen

Mikroprozessoren

Mikroprozessoren weisen meist einen oder mehrere unterschiedlich tiefe „Idle“-Zustände auf, welche durch spezielle Maschinenbefehle aktiviert werden und mittels Clock-Gating den Mikroprozessor in einen stromsparenden und leistungsreduzierten Modus versetzen. Mikroprozessoren für mobilen Einsatz wie die OMAP3 weisen neben softwareinduziertem Clock-Gating auch eigene Schaltungsteile auf, welche die aktuelle Verwendung von Teilen des Mikroprozessors, wie beispielsweise die Nutzung der DMA-Einheit, erkennen und momentan nicht benötigte Schaltungsteile wie den DMA-Controller mittels Clock-Gating temporär abschalten.

Taktteilung

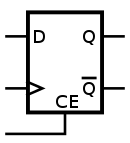

Clock-Gating kann auch zur gezielten Reduzierung der Verarbeitungsgeschwindigkeit verwendet werden, ohne weitere Taktsignale mit niedrigerer Frequenz zu benötigen. Dabei wird die Torschaltung periodisch angesteuert. Field Programmable Gate Arrays (FPGAs) weisen pro taktflankengesteuertem Flip-Flop einen Clock-Enable-Eingang auf, welcher eine Form von einfachem Clock-Gate darstellt. Bei inaktivem Clock-Enable ignoriert das Flip-Flop das Taktsignal. Wird nun der Clock-Enable-Eingang nur bei jeder zweiten Taktflanke periodisch aktiv geschaltet, führt dies zu einer Halbierung der Taktfrequenz am Flip-Flop.

Literatur

- Stephan Henzler: Power Management of Digital Circuits in Deep Sub-Micron CMOS Technologies (Springer Series in Advanced Microelectronics). 1. Auflage. Springer Netherlands, 2006, ISBN 978-90-481-7278-8 (Nachdruck 2010).