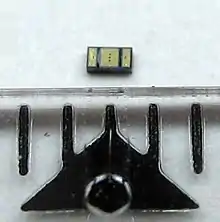

Chip Scale Package

Chip Scale Package (CSP, engl.; zu deutsch Gehäuse in der Größenordnung des Die) ist ein Chipgehäuse von integrierten Schaltungen, bei dem das Gehäuse maximal 20 % mehr Fläche als das Die ausmacht[1], wozu ersichtlich die Anschlüsse für SMD-Bestückung ohne Bonding mit dem Die verbunden werden müssen.[2]

Um die geringe Gehäuse-Grundfläche erreichen zu können, wird entweder die Flip-Chip-Montage (der Die wird nach Metallisierung seiner externen Kontakte umgekehrt auf das Board gelegt) oder die WLCSP-Methode genutzt. Bei der WLCSP-Methode wird zum Schutz des Die unten ein Schutzlack und von oben ein Plastik-Gehäuse aufgebracht.

Das CSP stellt somit eine Fortentwicklung des Ball Grid Array (BGA) dar, was auf Ideen von Mitarbeitern von Fujitsu und Hitachi Cable zurückgeht und erstmals von Mitsubishi Electric realisiert wurde.

Die mechanische Belastbarkeit des CSP ist im Vergleich zum BGA wesentlich geringer, da Kräfte von den Lötstellen direkt auf den Die übertragen werden.[3]

Eine Verkleinerung der Gehäuse ist etwa in der Medizintechnik, zum Beispiel für verschluckbare Diagnose-Geräte, und in der Hochfrequenztechnik für kurze Übertragungswege nützlich.

Einzelnachweise

- J-STD-012. Surface Mount Council. Abgerufen am 3. Juni 2016.

- CSP-Package. ITWissen. Abgerufen am 19. September 2013.

- Dr. Reza Ghaffarian: Chip Scale Review. NASA. 1999. Abgerufen am 25. November 2015.