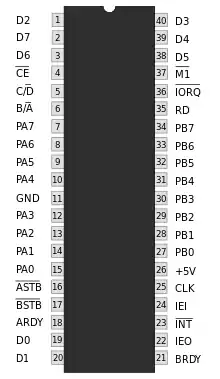

Z80 PIO

Das Parallel Input/Output (PIO)-Interface der Z80-Familie organisiert den parallelen Datentransfer zwischen Mikrocomputer und der Peripherie. Die Aktivitäten des PIO-Schaltkreises werden ausschließlich durch die CPU gesteuert. Somit ist es notwendig, dass beide Schaltkreise miteinander Signale austauschen können.

Da ein Prozessor für mehrere Peripheriegeräte zuständig ist, empfängt er auch mehrere Interrupt-Signale, kann allerdings immer nur eines pro Zeiteinheit abarbeiten. Somit muss eine Priorisierung gewährleistet sein. Der Interrupt-Requestor (= das den Interrupt anfordernde Gerät) muss dem System sowohl Beginn, als auch Ende seiner CPU-Inanspruchnahme signalisieren. Durch Verkettung (Daisy-Chain) über die Anschlüsse IEI-IEO können mehrere PIOs untereinander priorisiert werden.

- IEI (= Interrupt-Enable In): PIO wird berechtigt, Interruptvektor /INT an die CPU zu senden, wenn keine höher priorisierte PIO einen Interrupt aussendet.

- IEO (= Interrupt-Enable Out): Interrupt wird bearbeitet, niedriger priorisierte PIOs müssen warten.

Betriebsarten:

- Mode 0: Byteweise Ausgabe

- Mode 1: Byteweise Eingabe

- Mode 2: Bidirektionale Ein- und Ausgabe

- Mode 3: Einzelbitsteuerung (zur bitparallelen Ausgabe von Steuersignalen)