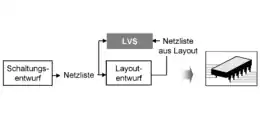

Layout Versus Schematic

Layout versus Schematic (LVS) ist ein Schritt bei der Layoutverifikation von integrierten Schaltkreisen. Er dient dazu, die Übereinstimmung des erzeugten Layouts mit der ursprünglichen Schaltung (schematic) sicherzustellen. Dabei erfolgt ein Netzlistenvergleich, bei dem die zum Layoutentwurf benutzte originale Netzliste mit einer ausschließlich aus dem Schaltungslayout extrahierten Netzliste verglichen wird.

Die Extraktion der Netzliste aus dem Layout erfolgt unter Nutzung eines Extraktionsfiles. Darin sind elementare Layoutstrukturen definiert, die beispielsweise Transistoren und Vias (vertical interconnect access, elektrische Verbindung zwischen zwei Leiterbahnebenen) abbilden, da deren Erkennung zur Netzlistengenerierung notwendig ist. Damit lassen sich die geometrischen Strukturen des Layouts daraufhin untersuchen, welche funktionalen Einheiten (Bauelemente und Verbindungsstrukturen) sie realisieren. Diese Informationen erlauben das Erzeugen einer Netzliste ausschließlich aus dem Schaltungslayout.