IOMMU

Eine I/O Memory Management Unit (I/O-MMU, oder kurz IOMMU) erweitert die I/O-Schnittstelle eines Mikroprozessors um eine Adressübersetzung und Zugriffsschutz bei Direct Memory Access (DMA).

Einsatz von I/O-MMUs war lange nur in High-End-Architekturen üblich, z. B. in einem PCI-Interface, welches die Firma Sun für ihre UltraSPARC-Prozessoren entworfen hatte. Im Rahmen der Erweiterung der AMD64-Architektur seitens AMD um Verfahren zur Virtualisierung wurde deren I/O-Hub darum ergänzt. Dieser Artikel bezieht sich vor allem auf die IOMMU für AMD64. AMD liefert seit 2009 Prozessoren mit IOMMU aus, zusammen mit HyperTransport 3.0.[1]

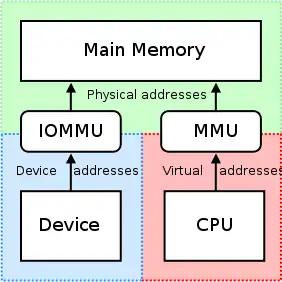

Das Verfahren ist prinzipiell vergleichbar mit einer Memory Management Unit (MMU) in multitaskingfähigen Mikroprozessoren. Der Unterschied liegt darin, dass die IOMMU nicht Teil der Speicheranbindung ist, sondern sich konzeptionell in der Northbridge befindet. Bei Zugriffen per DMA durch periphere Geräte werden Zieladressen im RAM dabei mit Hilfe einer von Systemsoftware kontrollierten, mehrstufigen Seitentabelle in alternative Adressen übersetzt.

Die IOMMU ermöglicht folgende Funktionen bei DMA:

- Effektivere Nutzung von 32-Bit-Geräten in 64-Bit-Umgebungen, insbesondere Zugriff auf Speicherbereiche oberhalb von 4 GiB.

- Zugriffsschutz beim Zugriff von Anwendungen auf bestimmte Geräte

- Zugriffsschutz beim Zugriff von virtuellen Maschinen auf bestimmte Geräte

Zugriffsschutz bedeutet, dass ohne IOMMU keine vollständige Isolation von Prozessen oder virtuellen Maschinen mehr gewährleistet werden kann, wenn direkter Zugriff auf DMA-fähige Geräte gewährt werden soll. Da DMA-Transfers praktisch auf beliebige Zieladressen im System zugreifen können, kann schädlicher Programmcode damit u. U. auch Speicherbereiche lesen oder überschreiben, die nicht Teil seines eigenen, virtuellen Adressraumes sind (siehe auch Sicherheitsprobleme bei Firewire).

Ähnliche Funktionen wie die der IOMMU finden sich auch in Prozessoren älterer Bauart. Bisher existiert in vielen Maschinen ein Graphics Aperture Remapping Table (GART) zur Adressübersetzung speziell für Grafikkarten im Accelerated Graphics Port (AGP). Die Secure-Virtual-Machine-Erweiterungen (SVM) in AMD-Prozessoren bieten auch ohne IOMMU rudimentären Zugriffsschutz durch einen Device Exclusion Vector (DEV), um Geräten den Zugang zum RAM vollständig zu verweigern. Mit passender Software-Unterstützung kann die IOMMU sowohl die Funktionen der GART als auch die des DEV ersetzen.

IOMMU ist kein wesentlicher Bestandteil von AMD-V. Wenn direkter Zugriff auf I/O-Ressourcen nicht durch einen VMM, sondern unmittelbar durch Gastsysteme auf der VM erfolgen soll, bietet sie gegenüber einem klassischen Trap-and-Simulate-Verfahren jedoch erhebliche Vorteile im Hinblick auf Sicherheit und Leistung. In vielen Anwendungen klassischer Systemvirtualisierung ist ein solcher direkter Zugriff aber nicht erforderlich.

Siehe auch

Quellen

- heise online: AMD: HyperTransport 3.0 für Multiprozessor-Server erst 2009. Abgerufen am 4. Oktober 2018 (deutsch).