I²S

Die I²S-Schnittstelle (Inter-IC Sound) wurde von Philips für serielle digitale Audiodaten bei der Kommunikation zwischen ICs entwickelt. Die Schnittstelle ist unidirektional. Die Takt-Generierung kann von beiden Busteilnehmern vorgenommen werden.

Übersicht

Die I²S-Schnittstelle wird typischerweise zur Übertragung digitaler Audiodaten verwendet. Diese können dabei in Form der Puls-Code-Modulation (PCM-Signal) vorliegen oder unter Verwendung entsprechender Steuercodes auch andersartig codiert sein. Beispielsweise werden über diese Schnittstelle auch digital codierte Datenströme nach Dolby E übertragen. Bei PCM-codierten Audiosignalen werden auf der I²S-Schnittstelle immer zwei Audiokanäle übertragen, was Stereoübertragung ermöglicht. Dabei wird abwechselnd ein Datenwort des rechten und des linken Audiokanals seriell übertragen. Bei nicht-PCM-codierten Audioübertragungen können auch mehr als zwei Audiokanäle übertragen werden.

Eine wesentliche Eigenschaft ist, dass diese Schnittstelle synchron ist. Dabei kann sowohl die Quelle, als auch die Senke den Takt erzeugen. Durch die vorhandenen Steuerleitungen wird auch die genaue zeitliche Ausrichtung der einzelnen abgetasteten Audiowerte festgelegt.

Die I²S-Schnittstelle wird häufig zur Anbindung von Analog-Digital-Wandlern und Digital-Analog-Wandlern an digitale Signalprozessoren (DSP) verwendet. Sie findet auch Verwendung als Schnittstelle, um Audiodaten zu eigenständigen digitalen Filtermodulen zu leiten.

Aufbau

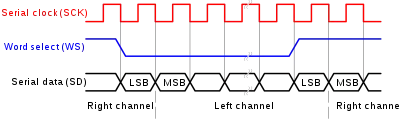

Die Schnittstelle besteht aus drei Signalleitungen, der Takt- (SCK), Daten- (SD) und der Word-Select-Leitung (WS). Die Word-Select-Leitung (WS) legt den genauen zeitlichen Rahmenstart und die Dauer eines seriell übertragenen Datenwortes fest. Des Weiteren definiert sie bei PCM-codierten Audiodaten, abhängig vom logischen Pegel, ob der gerade übertragene Audiowert dem rechten oder linken Audiokanal zugeordnet ist. Somit weist die WS-Leitung – die auch als Word-Clock bezeichnet wird – eine Frequenz auf, die genau der Abtastrate entspricht.

Die Kommunikation erfolgt immer nur in eine Richtung, d. h. Audiodaten werden beispielsweise von einem DSP zu einem Digital-Analog-Wandler gesendet, um darüber eine Sprachausgabe zu realisieren. Ein anderes Beispiel ist, dass ein Analog-Digital-Wandler die Signale eines Mikrofons in digitale Werte wandelt und danach über eine I²S-Schnittstelle an einen DSP schickt.

Eigenschaften

- Mindestens drei Signalleitungen (SCK, SD, WS), häufig noch eine zusätzliche Master-Clock mit der 128 bis 768-fachen Frequenz der Abtastrate.

- Keine Adressierung

- Keine bidirektionale Kommunikation

- Streng synchrone Übertragung ohne Pausen zwischen den einzelnen Werten

- Kombinierbarkeit von Bausteinen mit unterschiedlichen Wortlängen

Siehe auch

- I²C (Inter-Integrated Circuit): Ein anderer von Philips Semiconductors entwickelter serieller Datenbus.

Referenzen

- I2S bus specification. (PDF) Philips Semiconductors, 5. Juni 1996, archiviert vom Original am 2. Januar 2007; abgerufen am 28. Mai 2017 (englisch).