Extended Data Output Random Access Memory

Der EDO-RAM (Extended Data Output RAM, auch als Hyper Page Mode RAM bezeichnet) ist ein Halbleiterspeicher. Er gehört zur Gruppe der DRAMs und stellt eine geringfügige Weiterentwicklung des FPM-RAM (Fast Page Mode RAM) dar. Aufgrund seiner etwas erhöhten Datentransferrate begann er diesen etwa ab 1996 abzulösen.

Details

Der Unterschied zwischen EDO- und FPM-RAM macht sich nur beim sogenannten Pagemode-Betrieb bemerkbar, bei dem mehrere Datenbits aus derselben Speicherseite (Page) ausgelesen werden. In diesem Fall haben alle die gleiche Zeilenadresse (Row Address), jedoch unterschiedliche Spaltenadressen (Column Address). Das Protokoll lässt sich – sowohl beim FPM-RAM als auch beim EDO-RAM – dadurch vereinfachen, dass man die Übermittlung der gleich gebliebenen Zeilenadresse weglassen kann. Für das Auslesen von Daten aus der Speicherseite ist nun nur noch die Übertragung der Spaltenadresse notwendig.

Die Gültigkeit der Spaltenadresse wird durch eine fallende Flanke (vgl. Diagramm zum Lesezugriff) am externen CAS-Steuereingang (Column Address Strobe) gekennzeichnet. Nach einer gewissen Verzögerung stellt das DRAM die neuen Daten an seinen Ausgängen bereit. Das EDO-RAM unterscheidet sich in einem kleinen Detail vom FPM-RAM. Obwohl die für Rechner-Hauptplatinen („Mainboards“) bestimmten FPM- und EDO-RAM-Speichermodule physikalisch in die gleichen Steckplätze passen, funktioniert EDO-RAM entweder gar nicht in Mainboards ohne EDO-Unterstützung oder wird wie FPM angesprochen. Umgekehrt können jedoch fast immer Mainboards mit EDO-Unterstützung auch mit FPM-RAM betrieben werden. EDO-RAM gibt es mit Zugriffszeiten von 70 ns, 60 ns und 50 ns. Auf Mainboards, die den Front Side Bus mit 66 MHz Takt betreiben, können EDO-RAM mit 70 ns Zugriffszeit Probleme verursachen. Die Versionen mit maximal 32 MiB Kapazität haben die weiteste Verbreitung gefunden, wohingegen jene Versionen ab 64 MiB Kapazität sich gehäuft als inkompatibel zu den marktüblichen Mainboards erwiesen haben. Später gab es sogar Module mit 128 MiB, die aber wegen der damals schon vorhandenen Dominanz von SDRAM nicht mehr in großen Stückzahlen verkauft wurden.

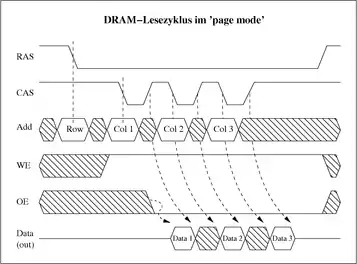

Die Ungültigkeit der Spaltenadresse wird beim älteren FPM-RAM durch die steigende Flanke der CAS-Steuerleitung signalisiert. Als Folge dessen deaktiviert das FPM-RAM seine Datentreiber, wodurch das zuvor gültige Datum von den externen Datenausgängen verschwindet (vgl. Diagramm zum page mode). Der Zustand der Datenausgänge bleibt solange undefiniert, bis durch Angabe einer neuen Spaltenadresse und eine fallende Flanke der CAS-Leitung der Vorgang wiederholt wird. Das FPM-RAM stellt die ausgelesenen Daten im Pagemode also nur für einen Bruchteil der Zykluszeit an seinen Ausgängen zur Verfügung.

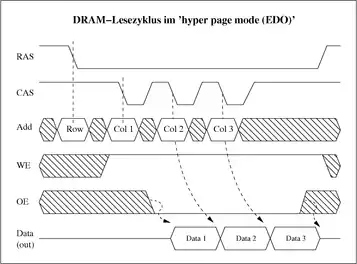

Beim neueren EDO-RAM wird hingegen die steigende Flanke der CAS-Steuerleitung ignoriert. Die Datentreiber bleiben aktiv, und die zuvor ausgelesene Dateninformation bleibt an den externen Datenausgängen solange bestehen, bis sie durch eine neue Information ersetzt wird (vgl. Diagramm zum EDO-Modus).

Durch diese Modifikation des Protokolls wird zunächst keinerlei Erhöhung der Datentransferrate erreicht. Es wird lediglich erreicht, dass das ausgelesene Datum während der gesamten Pagemode-Zykluszeit an den externen Datenausgängen zur Verfügung steht. Die verlängerte Verfügungszeit der ausgelesenen Daten beim EDO-RAM ermöglichte es, die mit der Weiterentwicklung der DRAMs einhergehende Geschwindigkeitssteigerung besser auszunutzen, indem man die Zykluszeit im Pagemode schrittweise weiter verringerte. Durch die innerhalb eines Zyklus verlängerte Verfügungszeit der Daten war trotz der verringerten Zykluszeit ein sicheres Auslesen der Daten gewährleistet. Der dadurch im Pagemode erreichte Leistungsgewinn des EDO-RAM wurde üblicherweise überschätzt und lag nur im Bereich weniger Prozente.

Spätere Entwicklungen

Beim BEDO-DRAM wurde die interne Steuerung des EDO-RAM modifiziert, sodass die Daten mehrerer aufeinander folgender Speicheradressen in einem einzigen Taktzyklus gemeinsam ausgelesen werden können. Diese Technik konnte sich am Markt nicht durchsetzen.

EDO-RAM wurde in nahezu allen Anwendungsbereichen durch SDRAM ersetzt.

Timing-Diagramme ausgewählter Kommandos (vereinfachte Darstellung)

- Lese- und Schreibzugriff

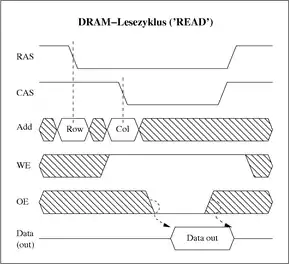

Lesezugriff („Read“)

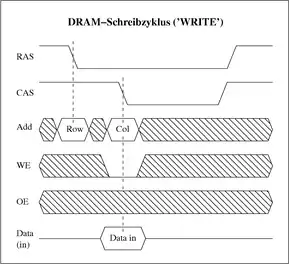

Lesezugriff („Read“) Schreibzugriff („Write“)

Schreibzugriff („Write“)

- Lesezugriff im page mode und hyper page mode (EDO)

Lesezugriff im „page mode“

Lesezugriff im „page mode“ Lesezugriff im „hyper page mode“ (EDO)

Lesezugriff im „hyper page mode“ (EDO)

- Refreshmodi

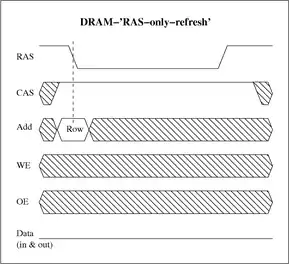

RAS-only-refresh

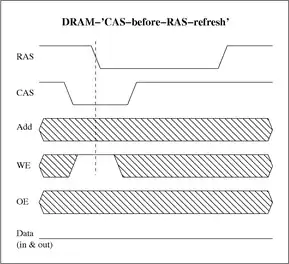

RAS-only-refresh CAS-before-RAS-refresh („CBR refresh“)

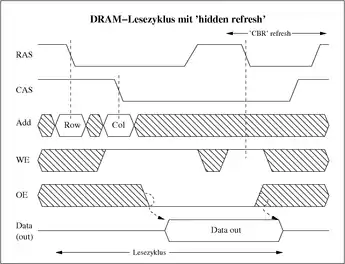

CAS-before-RAS-refresh („CBR refresh“) hidden-refresh im Lesezyklus

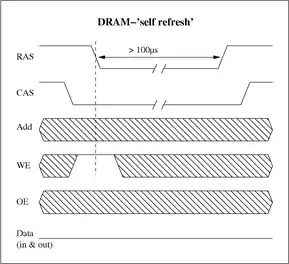

hidden-refresh im Lesezyklus self-refresh

self-refresh

Literatur

- SIEMENS Memory Components Data Book 10.96, Ordering No. B 166-H6557-G3-X-7600