DIBL-Effekt

Der DIBL-Effekt (von englisch drain-induced barrier lowering, dt. Drain(spannungs)-bedingte Potentialbarriereabsenkung) ist ein Kurzkanaleffekt in MOSFETs, der sich in seiner ursprünglichen Form auf eine Reduzierung der Schwellenspannung eines normal-sperrenden Transistors bei höherer Drainvorspannung (= Source-Drain-Spannung, ) bezieht. Bei einem klassischen planaren Feldeffekttransistor mit langem Kanal (ca. > 1 µm) entsteht die Verengung des Kanals weit genug entfernt vom Drain-Kontakt, so dass er durch die Kombination von Substrat und Gate elektrostatisch gegen den Drain abgeschirmt ist und die Schwellenspannung unabhängig von der Drainvorspannung ist. Bei kürzerem Kanal ist dies nicht mehr der Fall. Das Drain ist nah genug, um den Kanal zu beeinflussen, so dass eine hohe Drainvorspannung den Transistor vorzeitig einschalten kann.

Beschreibung

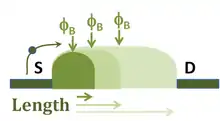

Die Ursache für die Schwellspannungsabnahme kann als Folge der Ladungsneutralität verstanden werden. Im Yau-Ladungsteilungsmodell[1] wird dies wie folgt beschrieben: Die kombinierte Ladung im Verarmungsbereich und die im Kanal des Bauelements ist über die Ladung der drei Elektroden ausgeglichen: Gate, Source und Drain. Wenn die Drainvorspannung erhöht wird, vergrößert sich der Verarmungsbereich des p-n-Übergangs zwischen Drain und Body, so dass er sich auch unter das Gate erstreckt. Damit übernimmt das Drain einen größeren Teil der Last der Ausgleichsladung des Verarmungsbereichs und gleichzeitig die Last des Gates reduziert. Infolgedessen behält die auf dem Gate vorhandene Ladung die Ladungsbilanz bei, indem sie mehr Ladungsträger in den Kanal zieht, was einer Senkung der Schwellenspannung der Vorrichtung entspricht.

Im Fall eines n-Kanal-Transistors zieht der Kanal mehr Elektronen an oder anderes gesagt, die Potentialbarriere für Elektronen im Kanal wird gesenkt. Daher wird zur Beschreibung dieser Phänomene der Begriff „Barrieresenkung“ (engl. barrier lowering) verwendet. Leider ist es nicht einfach, mit dem Barrieresenkungskonzept genaue Analyseergebnisse zu erzielen.

Die Barrierenabsenkung nimmt für kleiner werdende Kanallängen zu, selbst wenn die angelegte Drainvorspannung Null ist. Die Ursache liegt in den von Source- und Drain-Gebiet erzeugten p-n-Übergängen mit dem Body-Gebiet, denen integrierte Verarmungsgebiete zugeordnet sind. Diese werde bei kurzen Kanallängen zu nicht mehr vernachlässigbaren Anteilen im Ladungsausgleich des Bauelements, selbst wenn keine umgekehrte Vorspannung angelegt wird, um den Verarmungsbereich zu vergrößern. In der Praxis kann der DIBL-Wert wie folgt berechnet werden:

wobei (bzw. ) die Schwellspannung im Fall einer hohen Drainspannung (im Bereich der Versorgungsspannung) und (bzw. ) die Schwellspannung bei einer sehr niedrigen Drainspannung, typischerweise 0,05 V oder 0,1 V, ist. ist die Versorgungsspannung (bei hoher Drainspannung) und bei niedriger Drainspannung (für den linearen Teil der I-U-Kurve des Transistors). Das negative Vorzeichen in der Formel stellt einen positiven DIBL-Wert sicher, da immer kleiner als ist. Typischerweise wird der DIBL-Wert in der Einheit Millivolt je Volt (mV/V) angegeben.

Erweiterte Bedeutung

Darüber hinaus wird der Begriff DIBL auf weitere Drain-Spannungs-bezogene Effekte in der I-U-Kennlinie von MOSFETs bezogen. Wenn die Kanallänge reduziert wird, zeigen sich die Auswirkungen von DIBL im Unterschwellenbereich (engl. sub-threshold region, bei schwacher Inversion) zunächst als einfache Umsetzung in der Strom-Gatevorspannungs-Kurve mit einer Änderung der Drain-Spannung, die einfach modelliert werden kann. Bei kürzeren Kanallängen wird jedoch die Steigung der Strom-Gatevorspannungs-Kurve verringert, das bedeutet die gleiche Änderung des Drainstroms erfordert eine größere Änderung der Gatevorspannung. Bei extrem kurzen Längen kann das Bauelement nicht vollständig ausgeschaltet werden. Diese Effekte können nicht als Schwellenwertanpassung modelliert werden.[2]

Der DIBL-Effekt beeinflusst auch die Strom-Drainvorspannungs-Kurve im aktiven Modus eines MOSFETs. Er bewirkt einen Anstieg des Source-Drain-Stroms mit der Drainspannung, was den Ausgangswiderstand des MOSFET verringert. Diese Erhöhung tritt zusätzlich zum oben beschrieben Modulationseffekt der Kanallänge und kann nicht als Schwellenwerteinstellung modelliert werden.

DIBL kann auch die Betriebsfrequenz des Bauelements und somit der Gesamtschaltung reduzieren. Der relative Effekt kann über folgende Gleichung beschrieben werden:

wobei die Versorgungsspannung und die Schwellspannung sind.

Einzelnachweise

- Narain Arora: Mosfet Modeling for VLSI Simulation: Theory And Practice. World Scientific, 2007, ISBN 981-256-862-X, S. 197, Fig. 5.14 (eingeschränkte Vorschau in der Google-Buchsuche).

- Yannis Tsividis: Operational Modeling of the MOS Transistor. 2. Auflage. McGraw-Hill, New York 1999, ISBN 0-07-065523-5, S. 268; Fig. 6.11.