Cache-Kohärenz

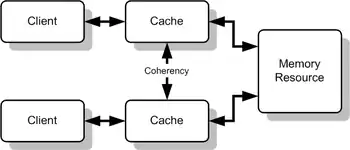

Durch die Sicherstellung von Cache-Kohärenz wird bei Mehrprozessorsystemen mit mehreren CPU-Caches verhindert, dass die einzelnen Caches für dieselbe Speicheradresse unterschiedliche (inkonsistente) Daten zurückliefern.

Eine temporäre Inkonsistenz zwischen Speicher und den Caches ist zulässig, sofern diese spätestens bei lesenden Zugriffen identifiziert und behoben wird. Inkonsistenzen werden z. B. durch das Rückschreibeverfahren (Write-Back) erzeugt, das im Gegensatz zu einem Durchschreibeverfahren (Write-Through) beim Schreiben in den Cache-Speicher nicht sofort den Hauptspeicher aktualisiert. Vergleiche dazu Cache-Konsistenz.

Cache-Kohärenz-Protokolle

Ein Cache-Kohärenz-Protokoll hat die Aufgabe, den Status eines gecachten Speicherblocks zu verfolgen. Im Wesentlichen gibt es zwei technische Grundlagen, auf denen ein solches Protokoll implementiert werden kann:[1]

- Verzeichnisbasiert (Directory-Based): Es wird eine zentrale Liste mit dem Status aller gecachten Blöcke geführt. Dort ist hinterlegt, welche Prozessoren zurzeit eine Read-only-Kopie (Status Shared) oder welcher Prozessor exklusiven Schreibzugriff (Status Exclusive) auf einen Block hat. Das Protokoll regelt den Übergang zwischen den verschiedenen Status und das Verhalten bei read miss, write miss bzw. data write back.

- Snoopingbasiert: Üblicherweise laufen Zugriffe auf den zentralen Speicher über ein gemeinsames Medium (z. B. Bus oder Switch). Alle angeschlossenen Cache Controller können dieses Medium beobachten und Schreib- oder Lesezugriffe auf Blöcke identifizieren, die sie selbst zwischengespeichert haben. Die genaue Reaktion des Controllers ist im Protokoll festgelegt.

Am häufigsten – sowohl bei verzeichnis- als auch snoopingbasiert – wird ein Write-Back-Invalidierungs-Protokoll (write-invalidate-protocol) eingesetzt, z. B. das Modified-Shared-Invalid Protokoll (MSI) bzw. dessen Erweiterungen MESI und MOESI. Alternativ dazu gibt es Write-Back-Update-Protokolle (vgl. Bus Snarfing), die allerdings zu einem erhöhten Busverkehr führen.

Die Wahl zwischen verzeichnis- und snoopingbasiert hängt u. a. auch von der Anzahl der beteiligten Prozessoren (Cache Controller) ab. Spätestens ab 64 Prozessoren müssen üblicherweise verzeichnisbasierte Protokolle benutzt werden, da die Bandbreite des Busses nicht ausreichend skaliert. Bei kleineren Installationen ist der snoopingbasierte Ansatz aufgrund der fehlenden zentralen Instanz etwas performanter.[2]

Bei Multiprozessorinstallation mit verteiltem Speicher (Distributed Memory) wird üblicherweise pro Speicher ein eigenes Verzeichnis geführt, damit der Verzeichniszugriff nicht zum Flaschenhals wird.[3]

Einzelnachweise

- John Hennessy, David Patterson: Computer Architecture. A Quantitative Approach., 4th Edition, Morgan Kaufmann Publishers, 2007, ISBN 978-0-12-370490-0 (engl.), S. 208ff

- John Hennessy, David Patterson: Computer Architecture. A Quantitative Approach., 4th Edition, Morgan Kaufmann Publishers, 2007, ISBN 978-0-12-370490-0 (engl.), S. 230

- John Hennessy, David Patterson: Computer Architecture. A Quantitative Approach., 4th Edition, Morgan Kaufmann Publishers, 2007, ISBN 978-0-12-370490-0 (engl.), S. 231

Literatur

- Thomas Rauber, Gudula Rünger: Parallele Programmierung Springer Verlag, 2007, ISBN 978-3-540-46549-2.

- David E. Culler: Parallel Computer Architecture, Morgan Kaufmann Publishers Inc., 1999, ISBN 1-55860-343-3.

- John Hennessy, David Patterson: Computer Architecture. A Quantitative Approach. 4th Edition, Morgan Kaufmann Publishers, 2007, ISBN 978-0-12-370490-0 (engl.).