Befehlszyklus

Der Befehlszyklus (englisch instruction cycle), auch als Fetch-Execute-Cycle bekannt, beschreibt den Ablauf der Verarbeitung eines Maschinenbefehls innerhalb eines synchronen Mikroprozessors.

Schema der Befehlsverarbeitung

Die Verarbeitung eines Maschinenbefehls erfolgt nach einem festen mehrstufigen Schema, das sich aus mehreren Maschinenzyklen zusammensetzt, welche üblicherweise mit dem CPU-Takt gleichlaufen. Je nach Prozessortyp und verwendetem Maschinenbefehlssatz findet man unterschiedliche Ausprägungen des im Folgenden vorgestellten Schemas.

1. Befehl laden

Zunächst muss der Befehl aus dem Hauptspeicher in den Prozessor geladen werden (englisch fetch instruction). Dazu benutzt der Prozessor den aktuellen Wert des Programmzählers, um die Stelle des Befehls im Hauptspeicher zu bestimmen. Der betreffende Befehl wird über den Datenbus in das Speicherdatenregister des Prozessors geladen und gelangt von dort aus in das Instruction Register (CIR).

2. Befehl dekodieren

In dieser Stufe (englisch decode instruction) werden der Befehlscode und die Operanden ermittelt. Außerdem wird ermittelt, wie die Operanden adressiert werden müssen.

Befehlsoperanden laden

Nach dem Dekodieren des Befehls werden die Operanden in den Prozessor geladen (englisch fetch operands). Die dafür erforderlichen internen Schritte sind abhängig von der jeweils verwendeten Adressierung.

3. Befehl ausführen

Nach dem Laden der benötigten Hauptspeicherinhalte in den Prozessor wird der Befehl gemäß dem Befehlscode ausgeführt (englisch execute). Beispielsweise werden logische Befehle mit Hilfe des Rechenwerks verarbeitet.

4. Ergebnis speichern

Das Ergebnis der Befehlsausführung wird im Hauptspeicher abgelegt (englisch store results). Handelte es sich beim letzten Befehl um einen Sprungbefehl, wird der Programmzähler entsprechend gesetzt. Anderenfalls erhält der Programmzähler die Adresse des nächsten Befehls.

Zusammenhang zwischen Befehlszyklus und Taktzyklus

Ein Maschinenprogramm besteht aus einer Menge von Maschinenbefehlen. Bei der Ausführung werden diese Befehle nacheinander in jeweils einem Befehlszyklus vom Prozessor abgearbeitet. Je nach Komplexität des Maschinenbefehlssatzes benötigt jeder Schritt des Befehlszyklus mehrere Taktzyklen. Um die Anzahl der abgearbeiteten Maschinenbefehle je Zeiteinheit zu erhöhen, können beispielsweise Taktfrequenzen erhöht oder eine Pipeline in den Prozessor integriert werden. Mit dem Pipelining kann die Bearbeitung aufeinander folgender Maschinenbefehle bis zu einem gewissen Grad parallelisiert werden (siehe auch Superskalarität).

Beispiel

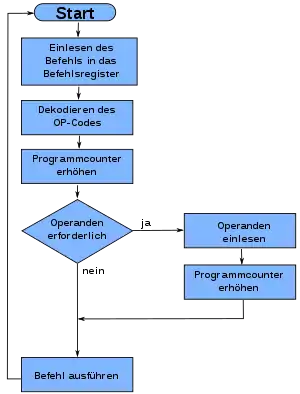

Das Schema rechts zeigt den Befehlszyklus eines typischen Mikrocontrollers.

- Lesen des neuen Befehls aus dem Speicher in das Befehlsregister (engl.: Instruction Register IR) gemäß der aktuellen Adresse des Befehlszählers (engl.: Program Counter PC)

- Dekodierung des Befehls

- Erhöhung des Inhalts vom PC um +1 (bzw. um die Größe des gerade geladenen Befehls, die besonders bei CISC-Architekturen variabel ist)

- Zugriff zu den Operanden, unter Umständen über einen erneuten Speicherlesevorgang und eine zugehörige Adressrechnung (bei indirekter Adressierung)

- Operationsdurchführung (z. B. Addition)

- Ergebnisabspeicherung

Literatur

- Randy H. Katz: Contemporary Logic Design. Benjamin/Cummings, Redwood City CA u. a. 1994, ISBN 0-8053-2703-7.

- Wolfgang Böge, Wilfried Plaßmann (Hrsg.): Vieweg-Handbuch Elektrotechnik. Grundlagen und Anwendungen für Elektrotechniker. 3., verbesserte und ergänzte Auflage. Vieweg, Wiesbaden 2004, ISBN 3-528-24944-7, S. 595.